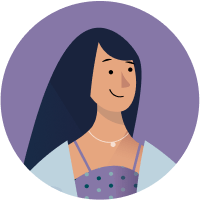

具体来看,该芯片堆叠封装(01)包括:

设置于第一走线结构(10)和第二走线结构(20)之间的第一芯片(101)和第二芯片(102);

所述第一芯片(101)的有源面(S1)面向所述第二芯片(102)的有源面(S2);第一芯片(101)的有源面(S1)包括第一交叠区域(A1)和第一非交叠区域(C1),第二芯片(102)的有源面(S2)包括第二交叠区域(A2)和第二非交叠区域(C2);

第一交叠区域(A1)与第二交叠区域(A2)交叠,第一交叠区域(A1)和第二交叠区域(A2)连接;

第一非交叠区域(C1)与第二走线结构(20)连接;

第二非交叠区域(C2)与第一走线结构(10)连接。

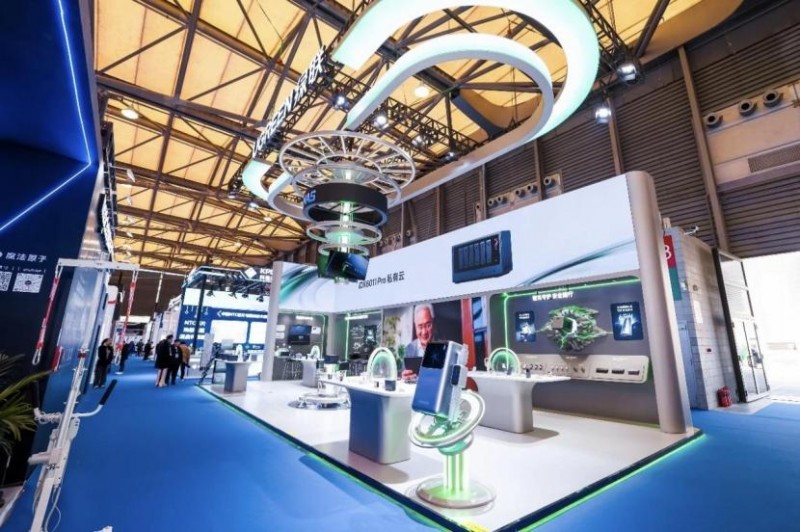

在前不久的华为2021年年报发布会上,华为轮值董事长郭平表示,未来华为可能会采用多核结构的芯片设计方案,以提升芯片性能。同时,采用面积换性能,用堆叠换性能,使得不那么先进的工艺也能持续让华为在未来的产品里面,能够具有竞争力。

值得一提的是,这是华为首次公开确认芯片堆叠技术。也就是说,可以通过增大面积,堆叠的方式来换取更高的性能,实现低工艺制程追赶高性能芯片的竞争力。

瑞小牛

瑞小牛

发表评论

电子邮件地址不会被公开。 必填项已用*标注